- 您现在的位置:买卖IC网 > Sheet目录317 > C8051F380-TB (Silicon Laboratories Inc)DEV KIT FOR C8051F38X

�� �

�

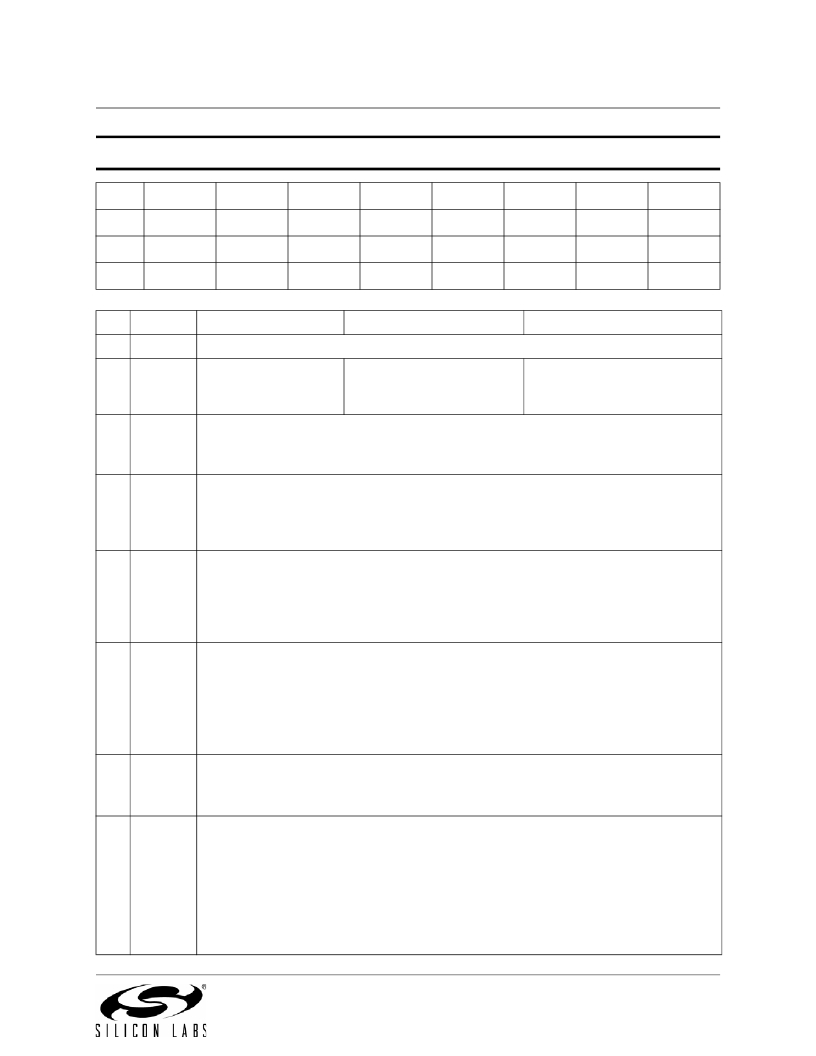

C8051F380/1/2/3/4/5/6/7/C�

�USB� Register� Definition� 21.20.� EINCSRL:� USB0� IN� Endpoint� Control� Low�

�Bit�

�Name�

�Type�

�Reset�

�7�

�R�

�0�

�6�

�CLRDT�

�W�

�0�

�5�

�STSTL�

�R/W�

�0�

�4�

�SDSTL�

�R/W�

�0�

�3�

�FLUSH�

�R/W�

�0�

�2�

�UNDRUN�

�R/W�

�0�

�1�

�FIFONE�

�R/W�

�0�

�0�

�INPRDY�

�R/W�

�0�

�USB� Register� Address� =� 0x11�

�Bit� Name� Description�

�Write�

�Read�

�7�

�Unused�

�Read� =� 0b.� Write� =� don’t� care.�

�6�

�CLRDT�

�Clear� Data� Toggle� Bit.� Software� should� write� 1� to�

�This� bit� always� reads� 0.�

�this� bit� to� reset� the� IN� End-�

�point� data� toggle� to� 0.�

�5�

�4�

�3�

�STSTL�

�SDSTL�

�FLUSH�

�Sent� Stall� Bit.�

�Hardware� sets� this� bit� to� 1� when� a� STALL� handshake� signal� is� transmitted.� The� FIFO� is�

�flushed,� and� the� INPRDY� bit� cleared.� This� flag� must� be� cleared� by� software.�

�Send� Stall.�

�Software� should� write� 1� to� this� bit� to� generate� a� STALL� handshake� in� response� to� an� IN�

�token.� Software� should� write� 0� to� this� bit� to� terminate� the� STALL� signal.� This� bit� has� no�

�effect� in� ISO� mode.�

�FIFO� Flush� Bit.�

�Writing� a� 1� to� this� bit� flushes� the� next� packet� to� be� transmitted� from� the� IN� Endpoint�

�FIFO.� The� FIFO� pointer� is� reset� and� the� INPRDY� bit� is� cleared.� If� the� FIFO� contains� mul-�

�tiple� packets,� software� must� write� 1� to� FLUSH� for� each� packet.� Hardware� resets� the�

�FLUSH� bit� to� 0� when� the� FIFO� flush� is� complete.�

�2�

�1�

�0�

�UNDRUN� Data� Underrun� Bit.�

�The� function� of� this� bit� depends� on� the� IN� Endpoint� mode:�

�ISO:� Set� when� a� zero-length� packet� is� sent� after� an� IN� token� is� received� while� bit�

�INPRDY� =� 0.�

�Interrupt/Bulk:� Set� when� a� NAK� is� returned� in� response� to� an� IN� token.�

�This� bit� must� be� cleared� by� software.�

�FIFONE� FIFO� Not� Empty.�

�0:� The� IN� Endpoint� FIFO� is� empty.�

�1.� The� IN� Endpoint� FIFO� contains� one� or� more� packets.�

�INPRDY� In� Packet� Ready.�

�Software� should� write� 1� to� this� bit� after� loading� a� data� packet� into� the� IN� Endpoint� FIFO.�

�Hardware� clears� INPRDY� due� to� any� of� the� following:� 1)� A� data� packet� is� transmitted.� 2)�

�Double� buffering� is� enabled� (DBIEN� =� 1)� and� there� is� an� open� FIFO� packet� slot.� 3)� If� the�

�endpoint� is� in� Isochronous� Mode� (ISO� =� 1)� and� ISOUD� =� 1,� INPRDY� will� read� 0� until� the�

�next� SOF� is� received.�

�Note:� An� interrupt� (if� enabled)� will� be� generated� when� hardware� clears� INPRDY� as� a� result� of� a�

�packet� being� transmitted.�

�Rev.� 1.4�

�199�

�发布紧急采购,3分钟左右您将得到回复。

相关PDF资料

C8051F912DK

KIT DEV FOR C8051F91X/C8051F90X

C8051F930-TB

BOARD TARGET/PROTO W/C8051F930

C8051T610DB24

DAUGHTER BOARD T610 24QFN SOCKET

C8051T630DB20

BOARD SOCKET DAUGHTER 20-QFN

CAN-100

BOARD EVAL RS232 100QFP

CANADAPT28

KIT ADAPTER CANDEMOBOARD 28PLCC

CAT24AA01WI-GT3

IC EEPROM SERIAL 1KB I2C 8SOIC

CAT24AA02WI-G

IC EEPROM SERIAL 2KB I2C 8SOIC

相关代理商/技术参数

C8051F381

制造商:SILABS 制造商全称:SILABS 功能描述:USB DRIVER CUSTOMIZATION

C8051F381-GM

功能描述:8位微控制器 -MCU USB-64K-Flash

RoHS:否 制造商:Silicon Labs 核心:8051 处理器系列:C8051F39x 数据总线宽度:8 bit 最大时钟频率:50 MHz 程序存储器大小:16 KB 数据 RAM 大小:1 KB 片上 ADC:Yes 工作电源电压:1.8 V to 3.6 V 工作温度范围:- 40 C to + 105 C 封装 / 箱体:QFN-20 安装风格:SMD/SMT

C8051F381-GMR

功能描述:8位微控制器 -MCU USB-Flash-64k-ADC RoHS:否 制造商:Silicon Labs 核心:8051 处理器系列:C8051F39x 数据总线宽度:8 bit 最大时钟频率:50 MHz 程序存储器大小:16 KB 数据 RAM 大小:1 KB 片上 ADC:Yes 工作电源电压:1.8 V to 3.6 V 工作温度范围:- 40 C to + 105 C 封装 / 箱体:QFN-20 安装风格:SMD/SMT

C8051F381-GQ

功能描述:8位微控制器 -MCU USB-64K-Flash

RoHS:否 制造商:Silicon Labs 核心:8051 处理器系列:C8051F39x 数据总线宽度:8 bit 最大时钟频率:50 MHz 程序存储器大小:16 KB 数据 RAM 大小:1 KB 片上 ADC:Yes 工作电源电压:1.8 V to 3.6 V 工作温度范围:- 40 C to + 105 C 封装 / 箱体:QFN-20 安装风格:SMD/SMT

C8051F381-GQR

功能描述:8位微控制器 -MCU USB-Flash-64k-ADC RoHS:否 制造商:Silicon Labs 核心:8051 处理器系列:C8051F39x 数据总线宽度:8 bit 最大时钟频率:50 MHz 程序存储器大小:16 KB 数据 RAM 大小:1 KB 片上 ADC:Yes 工作电源电压:1.8 V to 3.6 V 工作温度范围:- 40 C to + 105 C 封装 / 箱体:QFN-20 安装风格:SMD/SMT

C8051F382

制造商:SILABS 制造商全称:SILABS 功能描述:USB DRIVER CUSTOMIZATION

C8051F382-GQ

功能描述:8位微控制器 -MCU USB-Flash-32k-ADC

RoHS:否 制造商:Silicon Labs 核心:8051 处理器系列:C8051F39x 数据总线宽度:8 bit 最大时钟频率:50 MHz 程序存储器大小:16 KB 数据 RAM 大小:1 KB 片上 ADC:Yes 工作电源电压:1.8 V to 3.6 V 工作温度范围:- 40 C to + 105 C 封装 / 箱体:QFN-20 安装风格:SMD/SMT

C8051F382-GQR

功能描述:8位微控制器 -MCU USB-Flash-32k-ADC RoHS:否 制造商:Silicon Labs 核心:8051 处理器系列:C8051F39x 数据总线宽度:8 bit 最大时钟频率:50 MHz 程序存储器大小:16 KB 数据 RAM 大小:1 KB 片上 ADC:Yes 工作电源电压:1.8 V to 3.6 V 工作温度范围:- 40 C to + 105 C 封装 / 箱体:QFN-20 安装风格:SMD/SMT